基于ISO/IEC 14443 A協議的無源電子標簽數字集成電路設計

無源電子標簽,作為射頻識別(RFID)技術的核心組件,以其無需內置電源、體積小巧、成本低廉和壽命長久等優勢,在門禁管理、物流追蹤、移動支付和智能倉儲等領域得到了廣泛應用。其中,遵循ISO/IEC 14443 A協議的標簽因其在近場通信(NFC)生態系統中的關鍵地位而尤為重要。本文旨在探討基于該協議的無源電子標簽的數字集成電路(IC)設計,涵蓋其系統架構、關鍵模塊設計以及面臨的挑戰與趨勢。

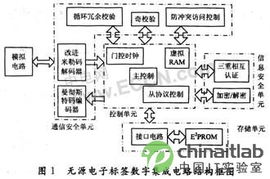

1. 系統架構概述

一個完整的基于14443 A協議的無源電子標簽數字集成電路,其核心是一個超低功耗的微控制器或專用狀態機。系統主要由以下幾個關鍵數字模塊構成:

- 射頻前端接口與解調器:接收來自讀寫器的13.56MHz載波信號,并通過包絡檢波等方式解調出曼徹斯特編碼的數字指令。

- 時鐘提取與恢復電路:從接收的射頻信號中提取時鐘基準,為整個數字系統提供同步時鐘,通常需要處理副載波(847kHz)的時鐘信息。

- 數字控制核心(狀態機/微控制器):這是標簽的“大腦”,負責協議層處理。它解析讀寫器的命令(如REQA、SELECT、HLTA等),訪問存儲器,并按照協議規范生成響應幀。為實現極低功耗,通常采用經過精心優化的硬連線狀態機或精簡指令集的8位微控制器內核。

- 存儲器控制器與存儲器:管理對EEPROM或鐵電存儲器(FRAM)的讀寫訪問,存儲唯一標識符(UID)、應用數據及系統配置信息。控制器需確保在電源波動(由射頻場強弱變化引起)下的讀寫可靠性。

- 負載調制器:根據數字核心的指令,通過控制負載電阻的變化,將響應數據以副載波調制的形式反向散射回讀寫器,完成通信。

- 電源管理與復位電路:對從射頻前端整流而來的不穩定電源進行穩壓和濾波,并產生可靠的上電復位信號,確保數字電路在苛刻的供電條件下穩定啟動和運行。

2. 關鍵數字模塊設計考量

2.1 低功耗設計

功耗是設計的首要約束。所有數字模塊必須采用低功耗設計技術:

- 亞閾值或近閾值設計:在性能允許的情況下,使晶體管工作在亞閾值區,可大幅降低動態和靜態功耗。

- 時鐘門控與電源門控:對非活躍模塊關閉時鐘甚至切斷電源。

- 異步電路設計:在局部采用異步邏輯,避免全局時鐘樹的功耗,并能更好地適應不穩定的電源環境。

- 體系結構優化:指令集和狀態機設計力求精簡,減少不必要的操作和翻轉活動。

2.2 協議處理狀態機設計

協議處理是數字核心的核心功能。設計一個高效、確定性的狀態機至關重要:

- 狀態機需精確實現14443 A協議第3部分(初始化和防沖突)及第4部分(傳輸協議)所規定的流程。

- 需要正確處理位級定時(如幀延遲時間FDT),這通常需要一個精密的定時器模塊。

- 防沖突算法(位幀防沖突)需要硬件加速支持,以實現快速的UID識別和選擇。

2.3 存儲器接口的可靠性設計

由于無源標簽的電源完全依賴外部射頻場,可能在讀寫操作期間發生波動甚至中斷。因此:

- 存儲器控制器需要實現原子操作和掉電保護機制,例如,在寫操作前將數據和地址暫存于易失性寄存器,并采用“寫-校驗”序列,防止數據損壞。

- 對于EEPROM,需精確控制高壓產生電路和編程時序。

2.4 抗干擾與魯棒性設計

標簽工作在復雜的電磁環境中,數字電路必須具備抗干擾能力:

- 對來自模擬前端的解調數據,需要進行數字濾波和毛刺消除。

- 復位電路需具有足夠的遲滯,防止電源輕微波動導致系統反復復位。

- 采用差錯檢測機制(如CRC校驗),確保命令和數據的完整性。

3. 設計流程與驗證

設計流程通常遵循標準的數字IC設計流程:

- 系統建模與算法驗證:使用高級語言(如C/Matlab)對協議處理算法和系統行為進行建模和驗證。

- 寄存器傳輸級(RTL)設計:使用硬件描述語言(如Verilog HDL)編寫所有數字模塊的代碼,重點在于低功耗描述。

- 功能仿真與綜合:進行大規模的功能仿真以驗證協議符合性,然后使用綜合工具將RTL代碼映射到目標工藝庫,并施加嚴格的面積和功耗約束。

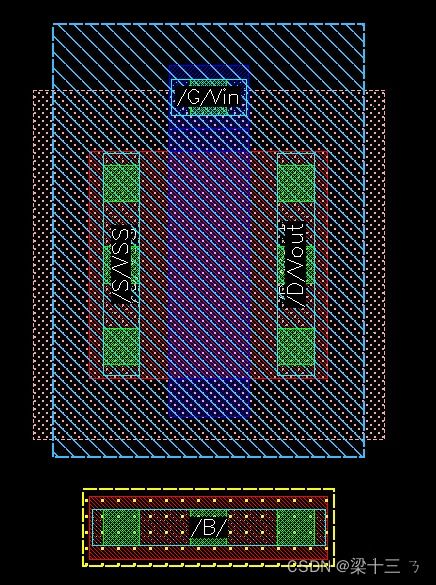

- 后端物理設計:包括布局布線、時鐘樹綜合、電源規劃等。需要特別關注模擬-數字混合信號的布局隔離,防止噪聲耦合。

- 后仿真與驗證:提取寄生參數后進行帶時序信息的門級仿真,以及最終的物理驗證(DRC, LVS)。

4. 挑戰與未來趨勢

- 功耗的極致降低:隨著應用場景的拓展(如嵌入式傳感標簽),對功耗的要求越發嚴苛,需要探索更先進的電路技術和新材料。

- 安全性增強:集成輕量級的密碼算法硬件加速引擎(如AES, ECC),以應對日益增長的安全需求,同時不能顯著增加功耗和面積。

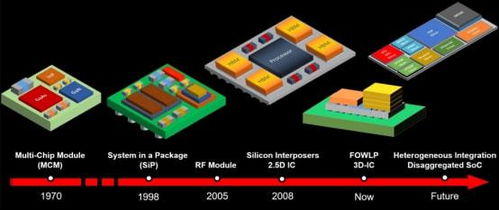

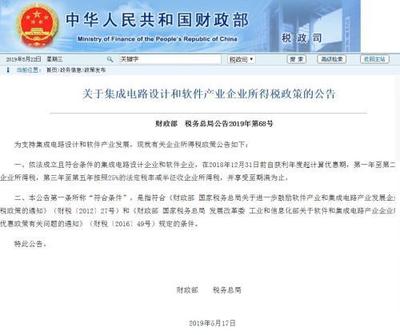

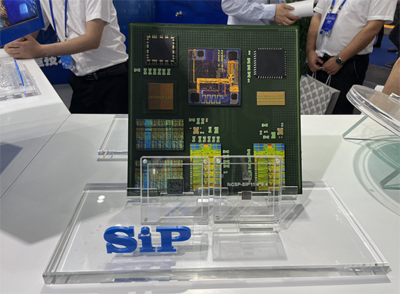

- 系統集成度:向更先進的工藝節點(如55nm, 40nm)遷移,以集成更多功能(傳感器接口、能量收集管理)并進一步降低成本。

- 設計自動化:開發針對超低功耗、不穩定電源環境的設計工具和標準單元庫,提升設計效率。

結論

基于ISO/IEC 14443 A協議的無源電子標簽數字集成電路設計是一個多學科交叉的工程挑戰,它平衡了協議復雜性、極致的功耗約束、成本控制和可靠性要求。通過精心的系統架構規劃、創新的低功耗電路設計以及嚴謹的設計驗證流程,能夠實現高性能、高可靠性的標簽芯片,為物聯網的末梢節點提供關鍵的感知與識別能力。隨著工藝進步和設計方法學的創新,未來的無源標簽芯片將變得更智能、更安全、更節能。

如若轉載,請注明出處:http://www.wearher.com.cn/product/67.html

更新時間:2026-01-20 23:05:18